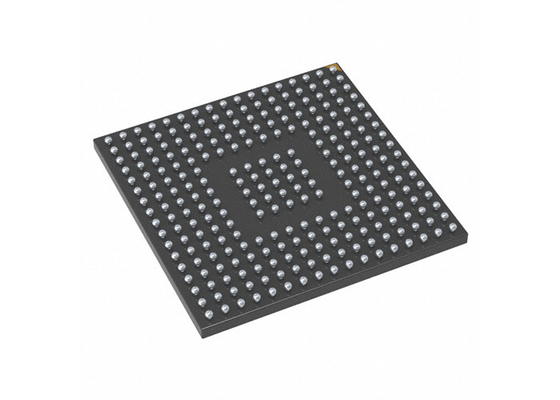

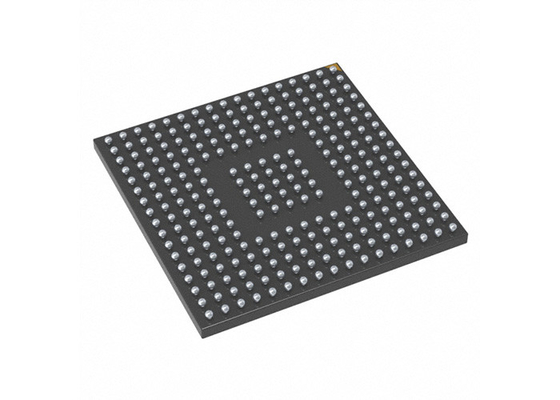

Chip Sirkuit Terpadu STM32H755IIK6 32-Bit Dual-Core ARM Mikrokontroler-MCU

Deskripsi Produk STM32H755IIK6

STM32H755IIK6 menawarkan tiga ADC, dua DAC, dua komparator daya sangat rendah, RTC berdaya rendah, pengatur waktu resolusi tinggi, 12 pengatur waktu 16-bit tujuan umum, dua pengatur waktu PWM untuk kontrol motor, lima pengatur waktu berdaya rendah, sebuah true random number generator (RNG), dan sel akselerasi kriptografis. Serta beragam I/O yang disempurnakan dan periferal yang terhubung ke bus APB, bus AHB, matriks bus multi-AHB 2x32-bit, dan interkoneksi AXI multi layer yang mendukung akses memori internal dan eksternal.

Spesifikasi DariSTM32H755IIK6

|

Jenis Memori Program

|

|

|

Ukuran RAM

|

|

|

Tegangan - Pasokan (Vcc/Vdd)

|

|

|

Pengonversi Data

|

|

|

Tipe Osilator

|

|

|

Suhu Operasional

|

|

|

Tipe Pemasangan

|

|

|

Paket / Kasus

|

|

|

Paket Perangkat Pemasok

|

|

Arm® Cortex®-M7 dengan FPU dari STM32H755IIK6

Arm® Cortex®-M7 dengan prosesor FPU presisi ganda adalah prosesor Arm generasi terbaru untuk sistem tertanam.Ini dikembangkan untuk menyediakan platform berbiaya rendah yang memenuhi kebutuhan implementasi MCU, dengan jumlah pin yang dikurangi dan konsumsi daya yang dioptimalkan, sambil memberikan kinerja komputasi yang luar biasa dan latensi interupsi yang rendah.

Prosesor Cortex®-M7 adalah fitur performa tinggi yang sangat efisien

Pipeline masalah ganda enam tahap

Prediksi cabang dinamis

Arsitektur Harvard dengan cache L1 (16 Kbytes I-cache dan 16 Kbytes Dcache)

Antarmuka AXI 64-bit

Antarmuka ITCM 64-bit

Antarmuka DTCM 2x32-bit

Antarmuka memori berikut didukung

Pisahkan bus Instruksi dan Data (Arsitektur Harvard) untuk mengoptimalkan latensi CPU

Antarmuka Tightly Coupled Memory (TCM) dirancang untuk akses SRAM yang cepat dan deterministik

Antarmuka AXI Bus untuk mengoptimalkan transfer Burst

Bus periferal AHB-Lite latensi rendah khusus (AHBP) untuk terhubung ke periferal.

FAQ

T. Apakah produk Anda asli?

A: Ya, semua produk asli, impor asli baru adalah tujuan kami.

T: Sertifikat apa yang Anda miliki?

J: Kami adalah Perusahaan Bersertifikat ISO 9001:2015 dan anggota ERAI.

T: Dapatkah Anda mendukung pesanan atau sampel dalam jumlah kecil? Apakah sampel gratis?

A: Ya, kami mendukung pesanan sampel dan pesanan kecil. Biaya sampel berbeda sesuai dengan pesanan atau proyek Anda.

T: Bagaimana cara mengirimkan pesanan saya?Apakah ini aman?

A: Kami menggunakan express untuk mengirim, seperti DHL, Fedex, UPS, TNT, EMS. Kami juga dapat menggunakan forwarder yang Anda sarankan. Produk akan dikemas dengan baik dan memastikan keamanan dan kami bertanggung jawab atas kerusakan produk pada pesanan Anda.

T: Bagaimana dengan waktu tunggu?

A: Kami dapat mengirimkan suku cadang stok dalam waktu 5 hari kerja. Jika tanpa stok, kami akan mengkonfirmasi waktu tunggu untuk Anda berdasarkan jumlah pesanan Anda.

Pesan Anda harus antara 20-3.000 karakter!

Pesan Anda harus antara 20-3.000 karakter! Silakan periksa email Anda!

Silakan periksa email Anda!  Pesan Anda harus antara 20-3.000 karakter!

Pesan Anda harus antara 20-3.000 karakter! Silakan periksa email Anda!

Silakan periksa email Anda!